Offres de Thèses, Stages et Post-docs

Rechercher...

nombre d'offres : 1

Réalisation de nanofils Si et SiGe pour les dispositifs Gate all around.

Date de début : 01/03/2019

Offre n° 1

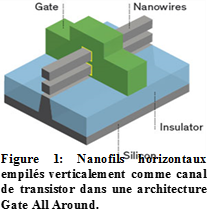

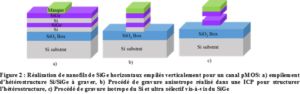

Les futures générations de dispositifs CMOS prévoient l’introduction d’architectures tridimensionnelles du type Gate all around (GAA) en remplacement du FiNFET. Un exemple de dispositif consiste à utiliser des nanofils parallèles au substrat et empilés verticalement comme canal de conduction, les matériaux de grille (le diélectrique et le métal) venant enrober ces nanofils (cf. figure 1).  Une étape clé du procédé de fabrication est la réalisation de ces nanofils (cf. Figure 2). Ces nanofils sont réalisés à partir d’hétérostructure Si/SiGe/Si/SiGe épitaxiée (cf. Fig. 2a). Cet empilement sera gravé de manière anisotrope dans des réacteurs de gravure plasma conventionnels de type ICP (inductively coupled plasma) (cf. Fig. 2b). Pour obtenir des nanofils à partir de ces empilements, il faut ensuite être capable de développer un procédé de gravure isotrope et sélectif permettant le retrait de la couche sacrificielle de SiGe par rapport au Si si l’on souhaite réaliser un canal en silicium de type n et vice et versa pour conserver un canal en SiGe de type p (cf. Fig. 2c). Cette étape est aujourd’hui le point bloquant de l’intégration.

Une étape clé du procédé de fabrication est la réalisation de ces nanofils (cf. Figure 2). Ces nanofils sont réalisés à partir d’hétérostructure Si/SiGe/Si/SiGe épitaxiée (cf. Fig. 2a). Cet empilement sera gravé de manière anisotrope dans des réacteurs de gravure plasma conventionnels de type ICP (inductively coupled plasma) (cf. Fig. 2b). Pour obtenir des nanofils à partir de ces empilements, il faut ensuite être capable de développer un procédé de gravure isotrope et sélectif permettant le retrait de la couche sacrificielle de SiGe par rapport au Si si l’on souhaite réaliser un canal en silicium de type n et vice et versa pour conserver un canal en SiGe de type p (cf. Fig. 2c). Cette étape est aujourd’hui le point bloquant de l’intégration.

L’objectif de ce projet de fin d’études de 6 mois est de développer des procédés plasma délocalisés permettant une gravure isotrope et sélective de la couche de SiGe par rapport à la couche de Si. Cette étude sera réalisée dans un réacteur industriel de gravure et le développement du procédé s’appuiera sur des techniques de caractérisation telles que l’ellipsométrie et la spectrométrie de photoélectrons X (XPS)

Ce travail sera effectué au Laboratoire des Technologies de la Microélectronique (LTM), laboratoire de recherche affilié au CNRS et l’Université Grenoble Alpes (UGA) situé sur le site du CEA-LETI-MINATEC à Grenoble.

- Mots clés : Engineering science, Electronics and microelectronics - Optoelectronics, LTM

- Laboratoire : LTM

- Code CEA : 1

- Contact : erwine.pargon@cea.fr

Contactez-nous

Contactez-nous Plan d’accès

Plan d’accès

Telecharger ma sélection

Telecharger ma sélection Réinitialiser

Réinitialiser